Question: Calculate the oscillation frequency for the

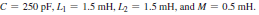

Calculate the oscillation frequency for the transistor Hartley circuit of Fig. 14.30 and the following circuit values:

> A 1-cm by -cm solar cell has a conversion efficiency of %. Determine the maximum power rating of the device.

> Referring to Fig. 16.11, if VDD = V for the varactor of Fig find the resonant frequency of the tank circuit if CC = pF and LT = mH.

> For the network of Fig. 4.136, determine: a. IB. b. IC. c. VCE. d. VC.

> Using Figa, compare the Q levels at a reverse bias potential of V and V. What is the ratio between the two? If the resonant frequency is 10 MHz, what is the bandwidth for each bias voltage? Compare the bandwidths obtained and compare their ra

> What region of VR would appear to have the greatest change in capacitance per change in reverse voltage for the diode of Fig. ? Be aware that it is a log-log scale. Then, for this region, determine the ratio of the change in capacitance to the chang

> Determine T1 for a varactor diode if C0 = 22 pF, TCC = 0.02%/ °C, and ΔC = 0.11 pF due to an increase in temperature above T0 = 25°C.

> At a reverse-bias potential of 4 V, determine the total capacitance for the varactor from Fig. a and calculate the Q value from Q = 1> (pf RS Ct) using a frequency of 10 MHz and Rs = Ω. Compare to the Q value determined from the chart of Fig

> Using Fig. a, determine the total capacitance at a reverse potential of V and 8 V and find the tuning ratio between these two levels. How does it compare to the tuning ratio for the ratio between reverse bias potentials of V and V?

> A full-wave rectifier (operating from a-Hz supply) drives a capacitor-filter circuit (C = mF), which develops V dc when connected to a -kΩ load. Calculate the output voltage ripple.

> A full-wave rectifier operating from the Hz ac supply produces a-V peak rectified voltage. If a-mF capacitor is used, calculate the ripple at a load of mA.

> A full-wave rectified voltage of V peak is connected to a@mF filter capacitor. What are the ripple and dc voltages across the capacitor at a load of mA?

> A full-wave rectified signal of V peak is fed into a capacitor filter. What is the voltage regulation of the filter if the output is V dc at full load?

> A simple capacitor filter fed by a full-wave rectifier develops V dc at ripple factor. What is the output ripple voltage (rms)?

> For the emitter follower network of Fig. 4.135 a. Find IB, IC, and IE. b. Determine VB, VC, and VE. c. Calculate VBC and VCE.

> What is the rms ripple voltage of a full-wave rectifier with output voltage 8 V dc?

> A half-wave rectifier develops V dc. What is the value of the ripple voltage?

> Determine the regulated output voltage from the circuit of Fig. 

> Determine the regulated voltage in the circuit of Fig.  with R1 =  Ω and R2 = ï€

> Determine the maximum value of load current at which regulation is maintained for the circuit of Fig. 

> Calculate the minimum input voltage of the full-wave rectifier and filter capacitor network in Fig. ï€±ï€µï€®ï€´ï€¶ï€ when connected to a load drawing ï

> Draw the circuit of a voltage supply comprised of a full-wave bridge rectifier, capacitor filter, and IC regulator to provide an output of + V.

> Determine the regulated voltage and circuit currents for the shunt regulator of Fig. .

> Calculate the regulated output voltage in the circuit of Fig. 

> What regulated output voltage results in the circuit of Fig. ?

> Determine the level of VE and IE for the network of Fig. 4.134.

> A filter circuit provides an output of V unloaded and V under full-load operation. Calculate the percentage voltage regulation.

> Calculate the output voltage and Zener diode current in the regulator circuit of Fig. 

> If the no-load output voltage for Problem 17 is V, calculate the percentage voltage regulation with a -kΩ load.

> Calculate the rms ripple voltage at the output of an RC filter section that feeds a @kΩ load when the filter input is V dc with -V rms ripple from a full-wave rectifier and capacitor filter. The RC filter section components are R = Ω and C =

> A simple capacitor filter has an input of V dc. If this voltage is fed through an RC filter section (R = Ω, C = mF), what is the load current for a load resistance of Ω?

> An RC filter stage (R = Ω, C = mF) is used to filter a signal of V dc with V rms operating from a full-wave rectifier. Calculate the percentage ripple at the output of the RC section for a-mA load. Also calculate the ripple of the filtere

> An RC filter stage is added after a capacitor filter to reduce the percentage of ripple to Calculate the ripple voltage at the output of the RC filter stage providing V dc.

> Calculate the percentage ripple for the voltage developed across a -mF filter capacitor when providing a load current of mA. The full-wave rectifier operating from the -Hz supply develops a peak rectified voltage of V.

> Calculate the size of the filter capacitor needed to obtain a filtered voltage with % ripple at a load of mA. The full-wave rectified voltage is V dc and the supply is Hz.

> A -mF capacitor provides a load current of mA at 8% ripple. Calculate the peak rectified voltage obtained from the -Hz supply and the dc voltage across the filter capacitor.

> Given VB = 4 V for the network of Fig. 4.133, determine: a. VE. b. IC. c. VC. d. VCE. e. IB. f. 

> Calculate the size of the filter capacitor needed to obtain a filtered voltage having % ripple at a load of mA. The full-wave rectified voltage is V dc, and the supply is Hz.

> What is the ripple factor of a sinusoidal signal having peak ripple of 2 V on an average of 50 V?

> For an FET Colpitts oscillator as in Fig. 14.26 and the following circuit values determine the circuit oscillation frequency:

> Calculate the frequency of a Wien bridge oscillator circuit (as in Fig. 14.23) when R = 10 kΩ and C = 2400 pF.

> Calculate the operating frequency of a BJT phase-shift oscillator as in Fig. 14.21b for R = 6 kΩ, C = 1500 pF, and RC = 18 kΩ.

> An FET phase-shift oscillator having gm = 6000 mS, rd = 36 kΩ, and feedback resistor R = 12 kΩ is to operate at 2.5 kHz. Select C for specified oscillator operation.

> For a circuit as in Fig. 14.11 and the following circuit values, calculate the circuit gain and the input and output impedances with and without feedback: RB = 600 kΩ, RE = 1.2 kΩ, RC = 4.7 kΩ, and b = 75. Use VCC = 16 V.

> Calculate the gain with and without feedback for an FET amplifier as in Fig. 14.7 for circuit values R1 = 800 kΩ, R2 = 200 Ω, Ro = 40 kΩ, RD = 8 kΩ, and gm = 5000 mS.

> Calculate the gain, input, and output impedances of a voltage-series feedback amplifier having A = - 300, Ri = 1.5 kΩ, Ro = 50 kΩ, and b = —1/15.

> If the gain of an amplifier changes from a value of —1000 by 10%, calculate the gain change if the amplifier is used in a feedback circuit having b = —1/20.

> Determine the range of possible values for VC for the network of Fig. 4.132 using the 1-MΩ potentiometer.

> Design a unijunction oscillator circuit for operation at (a) 1 kHz and (b) 150 kHz.

> Draw circuit diagrams of (a) a series-operated crystal oscillator and (b) a shunt-excited crystal oscillator.

> Calculate the oscillator frequency for an FET Hartley oscillator as in Fig. 14.29 for the following circuit values:

> For the transistor Colpitts oscillator of Fig. 14.27 and the following circuit values, calculate the oscillation frequency:

> Calculate the gain of a negative-feedback amplifier having A = —2000 and b = —1/10.

> For a reference voltage of 16 V, calculate the output voltage for an input of 11010 to the circuit of Problem 8.

> Sketch a five-stage ladder network using 15-kΩ and 30-kΩ resistors.

> Describe the operation of the circuit in Fig. 13.43.

> Sketch the output waveform for the circuit of Fig. 13.42.

> a. Determine the levels of IC and VCE for the network of Fig. 4.131. b. Change  to 135 (50% increase), and calculate the new levels of IC and VCE. c. Determine the magnitude of the percentage change in IC and VCE using the following equ

> Draw the circuit diagram of a zero-crossing detector using a 339 comparator stage with {12-V supplies.

> Draw the resulting output waveform for the circuit of Fig. 13.41.

> Draw a circuit diagram of a 311 op-amp showing an input of 10 V rms applied to the inverting input and the plus input to ground. Identify all pin numbers.

> What is the difference between open-collector and tri-state output?

> What is a data bus?

> Describe the signal conditions for current-loop and RS-232C interfaces.

> What is the lock range of the PLL circuit in Fig. 13.26b for

> What value of capacitor C1 is required in the circuit of Fig. 13.26b to obtain a center frequency of 100 kHz?

> Calculate the VCO free-running of Fig. 13. frequency for the circuit 26b with

> Sketch the output waveform for the circuit of Fig. 13.40.

> a. Compare levels of R' = RC + RE to RF> for the network of Fig. 4.131. b. Is the approximation ICQ ÷ V'>R' valid?

> If a transistor amplifier has more than one dc source, can the superposition theorem be applied to obtain the response of each dc source and algebraically add the results?

> Determine the capacitor needed in the circuit of Fig. 13.22 to obtain a 200-kHz output.

> What frequency range results in the circuit of Fig. 13.23 for

> Calculate the center frequency of a VCO using a 566 IC as in Fig. 13.22 for

> Sketch the input and output waveforms for a one-shot using a 555 timer triggered by a 10-kHz clock for

> Draw the circuit of a one-shot using a 555 timer to provide one time period of 20ms. If What value of C is needed?

> Sketch the circuit of a 555 timer connected as an astable multivibrator for operation at 350 kHz. Determine the value of capacitor C needed using

> What is the maximum count interval using a 12-stage counter operated at a clock rate of 20 MHz?

> How many count steps occur using a 12-stage digital counter at the output of an ADC?

> For a dual-slope converter, describe what occurs during the fixed time interval and the count interval.

> What voltage resolution is possible using a 12-stage ladder network with a 10-V reference voltage?

> For the voltage feedback network of Fig. 4.130, determine: a. IC. b. VC. c. VE. d. VCE.

> Draw the diagram of a 741 op-amp operated from {15-V supplies with Vi (-) = V and Vi (+) = + 5 V. Include terminal pin connections.

> Calculate the efficiency of the circuit of Problem 8 if the bias current is ICQ = 150 mA.

> A transformer-coupled class A amplifier drives a 16-Ω speaker through a 3.87:1 transformer. Using a power supply of VCC = 36 V, the circuit delivers 2 W to the load. Calculate: a. P(ac) across transformer primary. b. VL (ac). c. V(ac) at transformer prim

> Calculate the transformer turns ratio required to connect four parallel 16-Ω speakers so that they appear as an 8-kΩ effective load.

> What turns ratio transformer is needed to couple to an 8-Ω load so that it appears as an 8-kΩ effective load?

> A class A transformer-coupled amplifier uses a 25:1 transformer to drive a 4-Ω load. Calculate the effective ac load (seen by the transistor connected to the larger turns side of the trans- former).

> If the circuit of Fig. 12.35 is biased at its center voltage and center collector operating point, what is the input power for a maximum output power of 1.5 W?

> What maximum output power can be delivered by the circuit of Fig. 12.35 if RB is changed to 1.5 kΩ?

> What maximum power can a silicon transistor (TJmax = 200°C) dissipate into free air at an ambient temperature of 80°C?

> A 160-W silicon power transistor operated with a heat sink (uSA = 1.5°C>W) has uJC = 0.5°C>W and a mounting insulation of uCS = 0.8°C>W. What maximum power can be handled by the transistor at an ambient temperature of 80°C? (The junction temperature shou

> For the network of problem 27 a. Determine ICQ using the equation ICQ b. Compare with the results of problem 27 for ICQ. c. Compare R’ to RF/. d. Is the statement valid that the larger R’ is compa

> Determine the maximum dissipation allowed for a 100-W silicon transistor (rated at 25°C) for a derating factor of 0.6 W>°C at a case temperature of 150°C.

> For distortion readings of D2 = 0.15, D3 = 0.01, and D4 = 0.05, with I1 = 3.3 A and RC = 4 Ω, calculate the total harmonic distortion fundamental power component and total power.

> Calculate the second harmonic distortion for an output waveform having measured values of VCEmin = 2.4 V, VCEQ = 10 V, and VCEmax = 20 V.

> Calculate the total harmonic distortion for the amplitude components of Problem 19.

> Calculate the input power dissipated by the circuit of Fig. 12.35 if RB is changed to 1.5 kΩ.

> Calculate the harmonic distortion components for an output signal having fundamental amplitude of 2.1 V, second harmonic amplitude of 0.3 V, third harmonic component of 0.1 V, and fourth harmonic component of 0.05 V.

> For the power amplifier of Fig. 12.37, calculate: a. Po(ac). b. Pi(dc). c. %h. d. Power dissipated by both output transistors.

> If the input voltage to the power amplifier of Fig. 12.36 is 8-V rms, calculate: a. Pi(dc). b. Po(ac). c. %h. d. Power dissipated by both power output transistors.

> For the class B power amplifier of Fig. 12.36, calculate: a. Maximum Po(ac). b. Maximum Pi(dc). c. Maximum %h. d. Maximum power dissipated by both transistors.