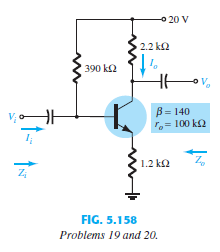

Question: Repeat Problem 19 with RE bypassed. Compare

> Repeat Problem 62 using the average values of the parameters of Fig. 5.92 with Av = - 180.

> Given the typical values of RL = 2.2 kΩ and hoe = 20 mS, is it a good approximation to ignore the effects of 1>hoe on the total load impedance? What is the percentage difference in total loading on the transistor using the followin

> Given the typical values of hie = 1 kΩ, hre = 2 * 10-4, and Av = - 160 for the input con- figuration of Fig. 5.185:

> For the feedback amplifier of Fig. 4.144 determine a. the base and collector current of each transistor. b. the base, emitter, and collector voltages of each transistor.

> Given IDSS = 6 mA and VP = - 4.5 V: a. Determine ID at VGS = - 2 and - 3.6 V. b. Determine VGS at ID = 3 and 5.5 mA.

> For a particular JFET if ID = 4 mA when VGS = —3 V, determine VP if IDSS = 12 mA.

> Given IDSS = 16 mA and VP = - 5 V, sketch the transfer characteristics using the data points of Table 6.1. Determine the value of ID at VGS = - 3 V from the curve, and compare it to the value determined using Shockley’s equation. Repeat the above for VGS

> Given IDSS = 9 mA and VP = - 4 V, determine ID when: a. VGS = 0 V. b. VGS = -2 V. c. VGS = -4 V. d. VGS = -6 V.

> Given IE (dc) = 1.2 mA, b = 120 and ro = 40 kΩ, sketch the following: a. Common-emitter hybrid equivalent model. b. Common-emitter re equivalent model. c. Common-base hybrid equivalent model. d. Common-base re equivalent model.

> Repeat problem 54 if a load resistance of 1.2 kΩ is introduced.

> Repeat problem 54 if a 22-Ω resistor is added between VE2 and ground.

> For the feedback pair of Fig. 5.182: a. Calculate the dc voltages VB1, VB2, VC1, VC2, VE1, and VE2. b. Determine the dc currents IB1, IC1, IB2, IC2, and IE2. c. Calculate the impedances Zi and Zo. d. Find the voltage gain Av = VO>VI. e. Determine the

> a. Given IDSS = 12 mA and VP = - 4 V, sketch the transfer characteristics for the JFET transistor. b. Sketch the drain characteristics for the device of part (a).

> Determine Av = VO>Vs for the network of Fig. 5.181 if the source has an internal resistance of 1.2 kΩ and the applied load is 10 kΩ.

> For the cascode amplifier of Fig. 4.143 determine a. the base and collector currents of each transistor. b. the voltages VB1, VB2, VE1, VC1, VE2, and VC2.

> Repeat problem 50 with a load resistor of 1.2 kΩ.

> For the Darlington network of Fig. 5.181: a. Determine the dc levels of VB1, VC1, VE2, VCB1, and VCE2. b. Find the currents IB1, IB2, and IE2. c. Calculate Zi and Zo. d. Determine the voltage gain Av = Vo/Vi and current gain Ai = Io>Ii.

> Calculate the ac voltage across a 10-kΩ load connected at the output of the circuit in Fig. 5.180.

> For the cascode amplifier circuit of Fig. 5.180, calculate the voltage gain Av and output voltage Vo.

> For the cascode amplifier circuit of Fig. 5.180, calculate the dc bias voltages VB1, VB2, and VC2.

> a. Calculate the voltage gain of each stage and the overall ac voltage gain for the BJT cascade amplifier circuit of Fig. 5.179. b. Find AiT = Io>Ii.

> For the BJT cascade amplifier of Fig. 5.179, calculate the dc bias voltages and collector current for each stage

> For the cascaded system of Fig. 5.178, determine: a. The loaded voltage gain of each stage. b. The total gain of the system, AvL and Avs. c. The loaded current gain of each stage. d. The total current gain of the system. e. How Zi is affected by the seco

> For the cascaded system of Fig. 5.177 with two identical stages, determine: a. The loaded voltage gain of each stage. b. The total gain of the system, Av and Avs. c. The loaded current gain of each stage. d. The total current gain of the system AiL=Io>

> Sketch the transfer characteristics of a p-channel enhancement-type MOSFET if VT = - 5 V and k = 0.45 * 10-3 A>V2.

> For the Darlington amplifier of Fig. 4.142 determine a. the level of D. b. the base current of each transistor. c. the collector current of each transistor. d. the voltages VC1, VC2, VE1, and VE2.

> Does the current of an enhancement-type MOSFET increase at about the same rate as a depletion- type MOSFET for the conduction region? Carefully review the general format of the equations, and if your mathematics background includes differential calculus,

> The maximum drain current for the 2N4351 n-channel enhancement-type MOSFET is 30 mA. Determine VGS at this current level if k = 0.06 * 10-3 A>V2 and VT is the maximum value.

> a. Determine the voltage gain AvL for the network of Fig. 5.173 with RL = 4.7 kΩ, 2.2 kΩ, and 0.5 kΩ. What is the effect of decreasing levels of RL on the voltage gain? b. How will Zi, Zo, and AvNL change with decreasing levels of RL?

> Given the transfer characteristics of Fig. 6.55, determine VT and k and write the general equation for ID.

> a. Given VGS (Th) = 4 V and ID(on) = 4 mA at VGS(on) = 6 V, determine k and write the general expression for ID in the format of Eq. (6.15). b. Sketch the transfer characteristics for the device of part (a). c. Determine ID for the device of part (a) at

> a. Sketch the transfer and drain characteristics of an n-channel enhancement-type MOSFET if VT = 3.5 V and k = 0.4 * 10-3 A>V2. b. Repeat part (a) for the transfer characteristics if VT is maintained at 3.5 V but k is increased by 100% to 0.8 *10-3 A>V2.

> a. Determine the voltage gain AvL for the network of Fig. 5.170 for RL = 4.7 kΩ, 2.2 kΩ, and 0.5 kΩ. What is the effect of decreasing levels of RL on the voltage gain? b. How will Zi, Zo, and AvNL change with decreasing values of RL?

> If the drain current for the 2N3797 MOSFET of Fig. 6.31 is 8 mA, what is the maximum permissible value of VDS utilizing the maximum power rating?

> Repeat problem 32 with the addition of an emitter resistor RE = 0.68 kΩ.

> For the network of Fig. 5.169: a. Determine Zi and Zo. b. Find Av.

> For the R–C-coupled amplifier of Fig. 4.141 determine a. the voltages VB, VC, and VE for each transistor. b. the currents IB, IC, and IE for each transistor

> For the network of Fig. 5.49: a. Derive the approximate equation for Av. b. Derive the approximate equations for Zi and Zo. c. Given RC = 2.2 kΩ, RF = 120 kΩ, RE = 1.2 kΩ, b = 90, and VCC = 10 V, calculate the magnitudes of Av, Zi, and Zo using the equat

> Given re = 10 Ω, b = 200, Av = - 160, and Ai = 19 for the network of Fig. 5.168, deter- mine RC, RF, and VCC.

> For the collector feedback configuration of Fig. 5.167: a. Determine re. b. Find Zi and Zo. c. Calculate Av.

> For the network of Fig. 5.166, determine Av.

> For the common-base configuration of Fig. 5.165: a. Determine re. b. Find Zi and Zo. c. Calculate Av.

> For the network of Fig. 5.164: a. Calculate IB and IC. b. Determine re. c. Determine Zi and Zo. d. Find Av.

> For the network of Fig. 5.163: a. Determine Zi and Zo. b. Find Av. c. Calculate VO if VI = 1 mV.

> For the network of Fig. 5.162: a. Determine re and bre. b. Find Zi and Zo. c. Calculate Av.

> For the network of Fig. 5.161: a. Determine re. b. Calculate VB, VCE, and VCB. c. Determine Zi and Zo. d. Calculate Av = VO>VI. e. Determine Ai = Io>Ii.

> For the network of Fig. 5.160: a. Determine re. b. Find Zi and Av.

> Using the characteristics of Fig. 4.121, design a voltage-divider configuration to have a satura- tion level of 10 mA and a Q-point one-half the distance between cutoff and saturation. The available supply is 28 V, and VE is to be one-fifth of VCC. The c

> For the network of Fig. 5.159, determine RE and RB if Av = - 10 and re = 3.8 Ω. Assume that Zb = bRE.

> For the network of Fig. 5.158: a. Determine re. b. Find Zi and Zo. c. Calculate Av. d. Repeat parts (b) and (c) with ro = 20 kΩ

> For the network of Fig. 5.157: a. Determine re. b. Find the dc voltages VB, VCB, and VCE. c. Determine Zi and Zo. d. Calculate Av = VO>VI.

> For the network of Fig. 5.156: a. Determine re. b. Calculate VB and VC. c. Determine Zi and Av = VO>VI.

> Determine VCC for the network of Fig. 5.155 if Av = - 160 and ro = 100 kΩ.

> For the network of Fig. 5.154: a. Determine re. b. Calculate Zi and Zo. c. Find Av. d. Repeat parts (b) and (c) with ro = 25 kΩ.

> For the network of Fig. 5.153: a. Calculate IB, IC, and re. b. Determine Zi and Zo. c. Calculate Av. d. Determine the effect of ro = 30 kΩ on Av.

> For the network of Fig. 5.152, determine VCC for a voltage gain of Av = - 160.

> For the network of Fig. 5.151: a. Determine Zi and Zo. b. Find Av. c. Repeat parts (a) and (b) with ro = 20 kΩ.

> Design a voltage-divider bias network using a supply of 24 V, a transistor with a beta of 110, and an operating point of ICQ = 4 mA and VCEQ = 8 V. Choose VE = 1/2 VCC. Use standard values.

> For the common-base configuration of Fig. 5.18, the dc emitter current is 3.2 mA and a is 0.99. Determine the following if the applied voltage is 48 mV and the load is 2.2 kΩ. a. re. b. Zi. c. Ic. d. Vo. e. Av. f. Ib.

> a. What is the expected amplification of a BJT transistor amplifier if the dc supply is set to zero volts? b. What will happen to the output ac signal if the dc level is insufficient? Sketch the effect on the waveform. c. What is the conversion efficienc

> Refer to the temperature controller of Fig. 17.13. a. Sketch the waveform of the full-wave rectified waveform across the SCR. b. What is the peak current through the heater when the SCR is “on” and has a short-circuit equivalent between anode and cathode

> Refer to the charging network of Fig. 17.12. a. Determine the dc level of the full-wave rectified signal if a 1:1 transformer is employed. b. If the battery in its uncharged state is sitting at 11 V, what is the anode-to-cathode voltage drop across SCR1?

> Fully explain why reduced values of R1 in Fig. 17.11 will result in an increased angle of conduction.

> In Fig. 17.10b, why is there very little loss in potential across the SCR during conduction?

> a. Based on Fig. 17.8, will a gate current of 50 mA fire the device at room temperature (25°C)? b. Repeat part (a) for a gate current of 10 mA. c. Will a gate voltage of 2.6 V trigger the device at room temperature? d. Is VG = 6 V, IG = 800 mA a good cho

> A. At high levels of gate current, the characteristics of an SCR approach those of what two- terminal device? B. At a fixed anode-to-cathode voltage less than V(BR)F*, what is the effect on the firing of the SCR as the gate current is reduced from its ma

> a. Will the network of Example 17.3 oscillate if VBB is changed to 10 V? What minimum value of VBB is required (VV a constant)? b. Referring to the same example, what value of R would place the network in the stable “on” state and remove the oscillatory

> Can Eq. (17.24) be derived exactly as shown from Eq. (17.23)? If not, what element is missing in Eq. (17.24)?

> Design an emitter-stabilized network at ICQ / ICsat = 10 mA, = 120, and RC = 4RE. Use standard values.

> Using the data provided in Example 17.3, determine the impedance of the PUT at the firing and valley points. Are the approximate open- and short-circuit states verified?

> Determine h and VG for a put with VBB = 20 V and RB1 = 3RB2.

> a. Referring to Fig. 17.57, determine the collector current above which the switching time does not change appreciably for RL = 1 kΩ and RL = 100 Ω. b. At IC = 6 mA, how does the ratio of switching times for RL = 1 kΩ and RL = 100 Ω compare to the ratio

> a. Sketch the maximum-power curve of PD = 200 mW on the graph of Fig. 17.56. List any noteworthy conclusions. b. Determine bdc (defined by IC>IF) for the system at VCE = 15 V, IF = 10 mA. c. Compare the results of part (b) with those obtained from Fig.

> Determine from Fig. 17.55 the ratio of LED output current to detector input current for an out- put current of 20 mA. Would you consider the device to be relatively efficient in its purpose?

> a. Determine from Fig. 17.54 the average change in ICEO per degree change in temperature for the range 25°C to 50°C. b. Can the results of part (a) be used to determine the level of ICEO at 35°C? Test your theory.

> a. Determine an average derating factor from the curve of Fig. 17.58 for the region defined by temperatures between —25°C and +50°C. b. Is it fair to say that for temperatures greater than room temperature (up to 100°C), the out- put current is somewhat

> Design a high-isolation OR-gate employing phototransistors and LEDs.

> For a phototransistor having the characteristics of Fig. 17.50, determine the photo induced base current for a radiant flux density of 5mW/cm2. If hfe = 40, find IC.

> Given the relaxation oscillator of Fig. 17.68: a. Find RB1 and RB2 at IE = 0 A. b. Determine VP, the voltage necessary to turn on the UJT. c. Determine whether R1 is within the permissible range of values defined by Eq. (17.8). d. Determine the frequency

> Determine RC and RB for a fixed-bias configuration if VCC = 12 V, = 80, and ICQ = 2.5 mA with VCEQ = 6 V. Use standard values.

> For a unijunction transistor with VBB = 20 V, h = 0.65, RB1 = 2 kΩ (IE = 0), and VD = 0.7 V, determine: a. RB2. b. RBB. c. VRB . d. VP.

> For the network of Fig. 17.40, in which V = 40 V, h = 0.6, VV = 1 V, IV = 8 mA, and IP = 10 mA, determine the range of R1 for the triggering network.

> For the network of Fig. 17.33, if C = 1 mF, find the level of R that will result in a 50% conduction period for the load in either direction if the turn-on voltage for the diac in either direction is 12 V and the applied sinusoidal signal has a peak valu

> Find the level of human body capacitance Cb that would result in a 45-degree phase shift between vi and vG for the network of Fig. 17.30.

> If VBR2 is 6.4 V, determine the range for VBR1 using Eq. (17.1).

> For the network of Fig. 17.28, if VBR = 6 V, V = 40 V, R = 10 kΩ, C = 0.2 mF, and VGK (firing potential) = 3 V, determine the time period between energizing the network and the turning on of the SCR.

> a. Using Fig. 17.24b, determine the minimum irradiance required to fire the device at room temperature (25°C). b. What percentage reduction in irradiance is allowable if the junction temperature is increased from 0°C (32°F) to 100°C (212°F)?

> a. In Fig. 17.22, if V= 50 V, determine the maximum possible value the capacitor C1 can charge to (VGK ÷ 0.7 V). b. Determine the approximate discharge time (5t) for R3 = 20 kΩ. c. Determine the internal resistance of the GTO if the rise time is one-ha

> For the network of Fig. 17.19 a. Write an equation for the voltage from gate to ground for the SCR. b. What is the voltage VGK when RS = R'? c. Find RS to establish a turn-on voltage of 2 V if R' = 10 kΩ. d. When the alarm turns on, what is the current t

> What is the suggested turn-off procedure for the network of Fig. 17.18?

> Given VC = 8 V for the network of Fig. 4.140, determine: a. IB. b. IC. c. d. VCE.

> What is the reactance of a 10@mF capacitor at a frequency of 1 kHz? For networks in which the resistor levels are typically in the kilohm range, is it a good assumption to use the short-circuit equivalence for the conditions just described? How about at

> Refer to the emergency-lighting system of Fig. 17.14. a. Sketch the waveform of the full-wave rectified signal across the bulb using a drop of 0.7 V during conduction of each diode. b. Determine the peak voltage across the capacitor C1 when the SCR1 is o

> a. For a varicap diode having the characteristics of Fig. determine the difference in capacitance between reverse-bias potentials of — V and — V. b. Determine the incremental rate of change (ΔC>ΔVr) at V = —8 V. How does this value compare with

> a. Determine the transition capacitance of a diffused junction varicap diode at a reverse potential of V if C(0) = pF and Vr = V. b. From the information of part (a), determine the constant K in Eq. (16.2).

> Using the characteristics of Fig(c), determine the reactance of the diode capacitor at a frequency of MHz and a reverse bias potential of V. Is it significant?

> Using the plot of Fig. a, a. What is the forward voltage at a current of mA (note the log scale) at room temperature (°C). b. What is the forward voltage at the same current as part (a) but a temperature of °C? c. What can be said about the e

> Determine the frequency of oscillation for the network of Fig. 16.50 if L = 5 mH, Rl = 10 Ω, and C = 1 mF.

> For E = 0.5 V and R = 51 Ω, sketch vT for the network of Fig. 16.49 and the tunnel diode of Fig. 16.44.

> Determine the stable operating points for the network of Fig. 16.48 if E = 2 V, R = 0.39 kΩ, and the tunnel diode of Fig. 16.44 is employed.